Hi,

I cannot locate any QPI sample code in the example. Was it possible for anyone to share me the sample code?

Thanks a bunch.

Hi,

I cannot locate any QPI sample code in the example. Was it possible for anyone to share me the sample code?

Thanks a bunch.

Thanks.

I tried the change the below code(under nrf_gpio.h), still no improvement. I was able to read the register using SPI master sample code from nordic nRF5_SDK_15.2.0_9412b96\examples\peripheral\spi

Do you know how can I use the qspi example(using nrf_drv_qspi_cinstr_xfer()) to read the register? I believe it will be great if I could at least test whether the register read is working before go into writing it.

__STATIC_INLINE void nrf_gpio_cfg_output(uint32_t pin_number)

{

nrf_gpio_cfg(

pin_number,

NRF_GPIO_PIN_DIR_OUTPUT,

NRF_GPIO_PIN_INPUT_DISCONNECT,

NRF_GPIO_PIN_NOPULL,

//old NRF_GPIO_PIN_S0S1,

NRF_GPIO_PIN_H0H1,

NRF_GPIO_PIN_NOSENSE);

}And when I take a closer look into the timing diagram I captured.

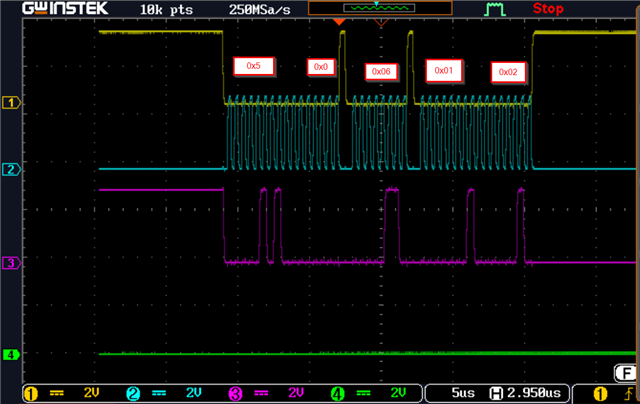

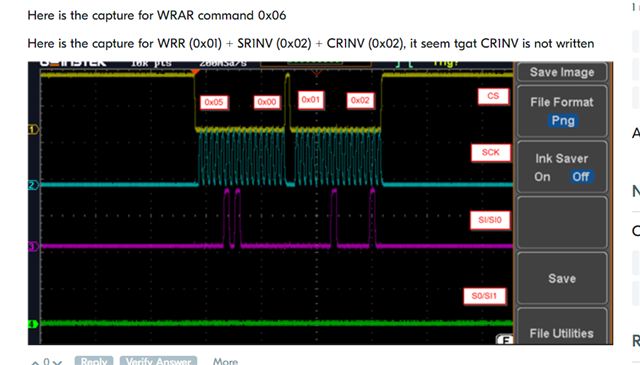

1) when using NRF_QSPI_CINSTR_LEN_2B, one frame is missing. We should have 0x5,0x00, 0x06(WREN), 0x01(WRSR), 0x02(SR1NV),0x02(CR1NV). But in fact, from the diagram I only get 0x5,0x00, 0x06(WREN), 0x01(WRSR), 0x02(SR1NV)

static void configure_memory()

{

uint16_t setting_spec[2] = {0x02,0x02};

uint32_t err_code;

nrf_qspi_cinstr_conf_t cinstr_cfg = {

.opcode = QSPI_STD_CMD_RSTEN,

.length = NRF_QSPI_CINSTR_LEN_1B,

.io2_level = true,

.io3_level = true,

.wipwait = true,

.wren = true

};

// Send reset enable

err_code = nrf_drv_qspi_cinstr_xfer(&cinstr_cfg, NULL, NULL);

APP_ERROR_CHECK(err_code);

// Send reset command

cinstr_cfg.opcode = QSPI_STD_CMD_RST;

err_code = nrf_drv_qspi_cinstr_xfer(&cinstr_cfg, NULL, NULL);

APP_ERROR_CHECK(err_code);

// Switch to qspi mode

cinstr_cfg.opcode = 0x01;

cinstr_cfg.length = NRF_QSPI_CINSTR_LEN_2B;

err_code = nrf_drv_qspi_cinstr_xfer(&cinstr_cfg, setting_spec, NULL);

APP_ERROR_CHECK(err_code);

}

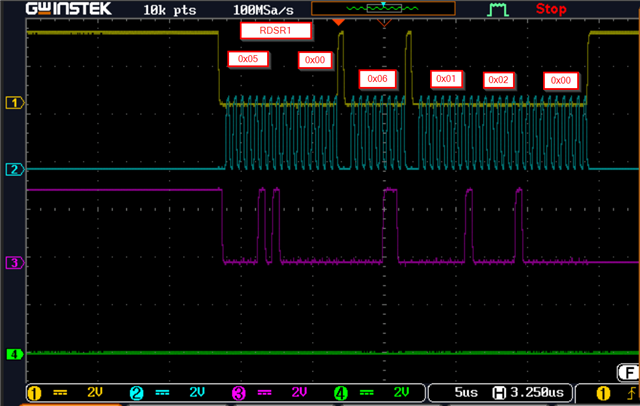

2) when using NRF_QSPI_CINSTR_LEN_3B, one frame is empty. We should have 0x5,0x00, 0x06(WREN), 0x01(WRSR), 0x02(SR1NV),0x02(CR1NV). But in fact, from the diagram I only get 0x5,0x00, 0x06(WREN), 0x01(WRSR), 0x02(SR1NV), 0x00(CR1NV) <---- missing data

static void configure_memory()

{

uint16_t setting_spec[2] = {0x02,0x02};

uint32_t err_code;

nrf_qspi_cinstr_conf_t cinstr_cfg = {

.opcode = QSPI_STD_CMD_RSTEN,

.length = NRF_QSPI_CINSTR_LEN_1B,

.io2_level = true,

.io3_level = true,

.wipwait = true,

.wren = true

};

// Send reset enable

err_code = nrf_drv_qspi_cinstr_xfer(&cinstr_cfg, NULL, NULL);

APP_ERROR_CHECK(err_code);

// Send reset command

cinstr_cfg.opcode = QSPI_STD_CMD_RST;

err_code = nrf_drv_qspi_cinstr_xfer(&cinstr_cfg, NULL, NULL);

APP_ERROR_CHECK(err_code);

// Switch to qspi mode

cinstr_cfg.opcode = 0x01;

cinstr_cfg.length = NRF_QSPI_CINSTR_LEN_3B;

err_code = nrf_drv_qspi_cinstr_xfer(&cinstr_cfg, setting_spec, NULL);

APP_ERROR_CHECK(err_code);

}

Maybe you need to use NRF_QSPI_CINSTR_LEN_2B

hI haakonsh

Thanks for the suggestion.

If I use NRF_QSPI_CINSTR_LEN_2B, I will only have one data sent out for example, my string is 0x02,0x02. It will sent out 0x02 only. Its already shown in my previous post.

Ahh my bad I think the length config should be NRF_QSPI_CINSTR_LEN_3B when you've got 2 data bytes in your custom commands