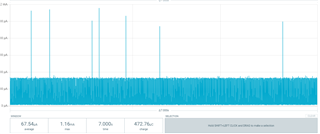

As the title states, my program (and a simple idle/hello world program for that matter) pull approximately 600-800 uA at idle. Same exact program, driver, and config on my nRF 52833 DK pulls about 8 uA at idle. I cannot figure out why this is. I suspect it has to do with the serial/UART interface and/or the network core? I noticed that even with "CONFIG_SERIAL=n" and "CONFIG_LOG=n" set in prj.conf I get output on UART/serial upon boot though it is from the bootloader. I did use the programmer tool to completely wipe the device (both network and app core) before I flashed it using West/Segger.

Output ("CONFIG_SERIAL=n" and "CONFIG_LOG=n") :

*** Booting Zephyr OS build v2.4.99-ncs2-2-g5049afda7b9f *** Flash regions Domain Permissions 00 01 0x00000 0x08000 Secure rwxl 02 63 0x08000 0x100000 Non-Secure rwxl Non-secure callable region 0 placed in flash region 1 with size 32. SRAM region Domain Permissions 00 03 0x00000 0x08000 Secure rwxl 04 63 0x08000 0x80000 Non-Secure rwxl Peripheral Domain Status 00 NRF_P0 Non-Secure OK 01 NRF_CLOCK Non-Secure OK 02 NRF_RTC0 Non-Secure OK 03 NRF_RTC1 Non-Secure OK 04 NRF_NFCT Non-Secure OK 05 NRF_NVMC Non-Secure OK 06 NRF_UARTE1 Non-Secure OK 07 NRF_UARTE2 Secure SKIP 08 NRF_TWIM2 Non-Secure OK 09 NRF_SPIM3 Non-Secure OK 10 NRF_TIMER0 Non-Secure OK 11 NRF_TIMER1 Non-Secure OK 12 NRF_TIMER2 Non-Secure OK 13 NRF_SAADC Non-Secure OK 14 NRF_PWM0 Non-Secure OK 15 NRF_PWM1 Non-Secure OK 16 NRF_PWM2 Non-Secure OK 17 NRF_PWM3 Non-Secure OK 18 NRF_IPC Non-Secure OK 19 NRF_VMC Non-Secure OK 20 NRF_FPU Non-Secure OK 21 NRF_EGU1 Non-Secure OK 22 NRF_EGU2 Non-Secure OK 23 NRF_DPPIC Non-Secure OK 24 NRF_REGULATORS Non-Secure OK 25 NRF_DCNF Secure SKIP 26 NRF_CTRLAP Secure SKIP 27 NRF_SPIM4 Non-Secure OK 28 NRF_WDT0 Non-Secure OK 29 NRF_WDT1 Non-Secure OK 30 NRF_COMP Non-Secure OK 31 NRF_LPCOMP Non-Secure OK 32 NRF_PDM0 Non-Secure OK 33 NRF_I2S0 Non-Secure OK 34 NRF_QSPI Non-Secure OK 35 NRF_NFCT Non-Secure OK 36 NRF_MUTEX Non-Secure OK 37 NRF_QDEC0 Non-Secure OK 38 NRF_QDEC1 Non-Secure OK 39 NRF_USBD Non-Secure OK 40 NRF_USBREGULATOR Non-Secure OK 41 NRF_P1 Non-Secure OK 42 NRF_OSCILLATORS Non-Secure OK 43 NRF_RESET Non-Secure OK 44 NRF_GPIOTE1 Non-Secure OK SPM: NS image at 0x8000 SPM: NS MSP at 0x200094d0 SPM: NS reset vector at 0xb3dd SPM: prepare to jump to Non-Secure image.

Output ("CONFIG_SERIAL=y" and "CONFIG_LOG=y" ) : *** Booting Zephyr OS build v2.4.99-ncs2-2-g5049afda7b9f ***

Flash regions Domain Permissions

00 01 0x00000 0x08000 Secure rwxl

02 63 0x08000 0x100000 Non-Secure rwxl

Non-secure callable region 0 placed in flash region 1 with size 32.

SRAM region Domain Permissions

00 03 0x00000 0x08000 Secure rwxl

04 63 0x08000 0x80000 Non-Secure rwxl

Peripheral Domain Status

00 NRF_P0 Non-Secure OK

01 NRF_CLOCK Non-Secure OK

02 NRF_RTC0 Non-Secure OK

03 NRF_RTC1 Non-Secure OK

04 NRF_NFCT Non-Secure OK

05 NRF_NVMC Non-Secure OK

06 NRF_UARTE1 Non-Secure OK

07 NRF_UARTE2 Secure SKIP

08 NRF_TWIM2 Non-Secure OK

09 NRF_SPIM3 Non-Secure OK

10 NRF_TIMER0 Non-Secure OK

11 NRF_TIMER1 Non-Secure OK

12 NRF_TIMER2 Non-Secure OK

13 NRF_SAADC Non-Secure OK

14 NRF_PWM0 Non-Secure OK

15 NRF_PWM1 Non-Secure OK

16 NRF_PWM2 Non-Secure OK

17 NRF_PWM3 Non-Secure OK

18 NRF_IPC Non-Secure OK

19 NRF_VMC Non-Secure OK

20 NRF_FPU Non-Secure OK

21 NRF_EGU1 Non-Secure OK

22 NRF_EGU2 Non-Secure OK

23 NRF_DPPIC Non-Secure OK

24 NRF_REGULATORS Non-Secure OK

25 NRF_DCNF Secure SKIP

26 NRF_CTRLAP Secure SKIP

27 NRF_SPIM4 Non-Secure OK

28 NRF_WDT0 Non-Secure OK

29 NRF_WDT1 Non-Secure OK

30 NRF_COMP Non-Secure OK

31 NRF_LPCOMP Non-Secure OK

32 NRF_PDM0 Non-Secure OK

33 NRF_I2S0 Non-Secure OK

34 NRF_QSPI Non-Secure OK

35 NRF_NFCT Non-Secure OK

36 NRF_MUTEX Non-Secure OK

37 NRF_QDEC0 Non-Secure OK

38 NRF_QDEC1 Non-Secure OK

39 NRF_USBD Non-Secure OK

40 NRF_USBREGULATOR Non-Secure OK

41 NRF_P1 Non-Secure OK

42 NRF_OSCILLATORS Non-Secure OK

43 NRF_RESET Non-Secure OK

44 NRF_GPIOTE1 Non-Secure OK

SPM: NS image at 0x8000

SPM: NS MSP at 0x200099a0

SPM: NS reset vector at 0xc1b1

SPM: prepare to jump to Non-Secure image.

*** Booting Zephyr OS build v2.4.99-ncs2-2-g5049afda7b9f ***

main entry point!

accel_entry_point!

main entry point!

temp_entry_point!

Running on arm!

Temp Sensor 0x20008390 name HDC2022 is ready!

START OF temp_entry_point LOOP

START OF accel_entry_point LOOP

Waiting for a threshold event

trigger_handler fired!

1072693248.00 g: #

END OF accel_entry_point LOOP

START OF accel_entry_point LOOP

Waiting for a threshold event

Note I get about the same idle current draw whether SERIAL and LOG is set to yes or no.

Here is my project config and other relevant info:

I am building using nrf5340dk_nrf5340_cpuappns.

nrf5340dk_nrf5340_cpuappns.overlay : &i2c1 {

compatible = "nordic,nrf-twim";

status = "okay";

sda-pin = < 30 >;

scl-pin = < 31 >;

clock-frequency = <I2C_BITRATE_STANDARD>;

adi_adxl372: adxl372@53 {

compatible = "adi,adxl372";

reg = <0x53>;

label = "ADXL372";

int1-gpios = <&gpio0 11 0>;

};

ti_hdc20x0: hdc20x0@41 {

compatible = "ti,hdc20x0";

reg = <0x41>;

label = "HDC2022";

drdy-gpios = <&gpio0 12 GPIO_ACTIVE_LOW>;

};

};

prj.conf : CONFIG_ASSERT=y # validation

CONFIG_STDOUT_CONSOLE=y

CONFIG_LOG=n

CONFIG_SERIAL=n

CONFIG_SENSOR_LOG_LEVEL_WRN=y

CONFIG_I2C=y

CONFIG_I2C_NRFX=y

CONFIG_SENSOR=y

CONFIG_GPIO=y

CONFIG_ADXL372=y

CONFIG_ADXL372_I2C=y

CONFIG_ADXL372_PEAK_DETECT_MODE=y

CONFIG_ADXL372_TRIGGER_GLOBAL_THREAD=y #THIS ENABLES ADXL372_TRIGGER (see Kconfig.txt for more!)

#CONFIG_ADXL372_TRIGGER_OWN_THREAD=y #THIS ENABLES ADXL372_TRIGGER (see Kconfig.txt for more!)

CONFIG_HDC20X0=y

# Zephyr Device Power Management

CONFIG_DEVICE_POWER_MANAGEMENT=y

CONFIG_PM=y

CMakeLists.txt : cmake_minimum_required(VERSION 3.13.1)

set(TEST_DTC_OVERLAY_FILE

${CMAKE_CURRENT_SOURCE_DIR}/nrf5340dk_nrf5340_cpuappns.overlay

)

set(PRJ_CONF_FILE

prj.conf

${CMAKE_CURRENT_LIST_DIR}/prj.conf

)

find_package(Zephyr REQUIRED HINTS $ENV{ZEPHYR_BASE})

project(hub_control)

zephyr_include_directories(include)

FILE(GLOB app_sources src/*.c)

target_sources(app PRIVATE ${app_sources})

Zephyr.dts : /dts-v1/;

/ {

#address-cells = < 0x1 >;

#size-cells = < 0x1 >;

model = "Nordic NRF5340 DK NRF5340 Application";

compatible = "nordic,nrf5340-dk-nrf5340-cpuapp";

chosen {

zephyr,flash-controller = &flash_controller;

zephyr,entropy = &cryptocell_sw;

zephyr,console = &uart0;

zephyr,shell-uart = &uart0;

zephyr,uart-mcumgr = &uart0;

zephyr,bt-mon-uart = &uart0;

zephyr,bt-c2h-uart = &uart0;

zephyr,ipc_shm = &sram0_shared;

zephyr,sram = &sram0_ns;

zephyr,flash = &flash0;

zephyr,code-partition = &slot0_ns_partition;

};

aliases {

led0 = &led0;

led1 = &led1;

led2 = &led2;

led3 = &led3;

sw0 = &button0;

sw1 = &button1;

sw2 = &button2;

sw3 = &button3;

};

soc {

#address-cells = < 0x1 >;

#size-cells = < 0x1 >;

compatible = "nordic,nRF5340-CPUAPP-QKAA", "nordic,nRF5340-CPUAPP", "nordic,nRF53", "simple-bus";

interrupt-parent = < &nvic >;

ranges;

nvic: interrupt-controller@e000e100 {

compatible = "arm,v8m-nvic";

reg = < 0xe000e100 0xc00 >;

interrupt-controller;

#interrupt-cells = < 0x2 >;

arm,num-irq-priority-bits = < 0x3 >;

phandle = < 0x1 >;

};

systick: timer@e000e010 {

compatible = "arm,armv8m-systick";

reg = < 0xe000e010 0x10 >;

status = "disabled";

};

sram0: memory@20000000 {

compatible = "mmio-sram";

reg = < 0x20000000 0x80000 >;

};

sram1: memory@21000000 {

compatible = "mmio-sram";

reg = < 0x21000000 0x10000 >;

};

peripheral@40000000 {

#address-cells = < 0x1 >;

#size-cells = < 0x1 >;

ranges = < 0x0 0x40000000 0x10000000 >;

flash_controller: flash-controller@39000 {

compatible = "nordic,nrf53-flash-controller";

reg = < 0x39000 0x1000 >;

#address-cells = < 0x1 >;

#size-cells = < 0x1 >;

label = "NRF_FLASH_DRV_NAME";

flash0: flash@0 {

compatible = "soc-nv-flash";

label = "NRF_FLASH";

erase-block-size = < 0x1000 >;

write-block-size = < 0x4 >;

reg = < 0x0 0x100000 >;

partitions {

compatible = "fixed-partitions";

#address-cells = < 0x1 >;

#size-cells = < 0x1 >;

boot_partition: partition@0 {

label = "mcuboot";

reg = < 0x0 0x10000 >;

};

slot0_partition: partition@10000 {

label = "image-0";

reg = < 0x10000 0x40000 >;

};

slot0_ns_partition: partition@50000 {

label = "image-0-nonsecure";

reg = < 0x50000 0x30000 >;

};

slot1_partition: partition@80000 {

label = "image-1";

reg = < 0x80000 0x40000 >;

};

slot1_ns_partition: partition@c0000 {

label = "image-1-nonsecure";

reg = < 0xc0000 0x30000 >;

};

scratch_partition: partition@f0000 {

label = "image-scratch";

reg = < 0xf0000 0xa000 >;

};

storage_partition: partition@fa000 {

label = "storage";

reg = < 0xfa000 0x6000 >;

};

};

};

};

adc: adc@e000 {

compatible = "nordic,nrf-saadc";

reg = < 0xe000 0x1000 >;

interrupts = < 0xe 0x1 >;

status = "okay";

label = "ADC_0";

#io-channel-cells = < 0x1 >;

};

dppic: dppic@17000 {

compatible = "nordic,nrf-dppic";

reg = < 0x17000 0x1000 >;

status = "okay";

label = "DPPIC";

};

egu0: egu@1b000 {

compatible = "nordic,nrf-egu";

reg = < 0x1b000 0x1000 >;

interrupts = < 0x1b 0x1 >;

status = "okay";

};

egu1: egu@1c000 {

compatible = "nordic,nrf-egu";

reg = < 0x1c000 0x1000 >;

interrupts = < 0x1c 0x1 >;

status = "okay";

};

egu2: egu@1d000 {

compatible = "nordic,nrf-egu";

reg = < 0x1d000 0x1000 >;

interrupts = < 0x1d 0x1 >;

status = "okay";

};

egu3: egu@1e000 {

compatible = "nordic,nrf-egu";

reg = < 0x1e000 0x1000 >;

interrupts = < 0x1e 0x1 >;

status = "okay";

};

egu4: egu@1f000 {

compatible = "nordic,nrf-egu";

reg = < 0x1f000 0x1000 >;

interrupts = < 0x1f 0x1 >;

status = "okay";

};

egu5: egu@20000 {

compatible = "nordic,nrf-egu";

reg = < 0x20000 0x1000 >;

interrupts = < 0x20 0x1 >;

status = "okay";

};

i2s0: i2s@28000 {

compatible = "nordic,nrf-i2s";

#address-cells = < 0x1 >;

#size-cells = < 0x0 >;

reg = < 0x28000 0x1000 >;

interrupts = < 0x28 0x1 >;

status = "disabled";

label = "I2S_0";

};

ipc: ipc@2a000 {

compatible = "nordic,nrf-ipc";

reg = < 0x2a000 0x1000 >;

interrupts = < 0x2a 0x1 >;

status = "okay";

label = "IPC";

};

kmu: kmu@39000 {

compatible = "nordic,nrf-kmu";

reg = < 0x39000 0x1000 >;

interrupts = < 0x39 0x1 >;

status = "okay";

};

pdm0: pdm@26000 {

compatible = "nordic,nrf-pdm";

reg = < 0x26000 0x1000 >;

interrupts = < 0x26 0x1 >;

status = "disabled";

label = "PDM_0";

};

regulators: regulator@4000 {

compatible = "nordic,nrf-regulators";

reg = < 0x4000 0x1000 >;

status = "okay";

};

vmc: vmc@81000 {

compatible = "nordic,nrf-vmc";

reg = < 0x81000 0x1000 >;

status = "okay";

};

uart0: uart@8000 {

compatible = "nordic,nrf-uarte";

reg = < 0x8000 0x1000 >;

interrupts = < 0x8 0x1 >;

status = "okay";

label = "UART_0";

current-speed = < 0x1c200 >;

tx-pin = < 0x14 >;

rx-pin = < 0x16 >;

rts-pin = < 0x13 >;

cts-pin = < 0x15 >;

};

uart1: uart@9000 {

compatible = "nordic,nrf-uarte";

reg = < 0x9000 0x1000 >;

interrupts = < 0x9 0x1 >;

status = "disabled";

label = "UART_1";

};

uart2: uart@b000 {

compatible = "nordic,nrf-uarte";

reg = < 0xb000 0x1000 >;

interrupts = < 0xb 0x1 >;

status = "disabled";

label = "UART_2";

};

uart3: uart@c000 {

compatible = "nordic,nrf-uarte";

reg = < 0xc000 0x1000 >;

interrupts = < 0xc 0x1 >;

status = "disabled";

label = "UART_3";

};

i2c0: i2c@8000 {

#address-cells = < 0x1 >;

#size-cells = < 0x0 >;

reg = < 0x8000 0x1000 >;

clock-frequency = < 0x186a0 >;

interrupts = < 0x8 0x1 >;

status = "disabled";

label = "I2C_0";

};

i2c1: i2c@9000 {

#address-cells = < 0x1 >;

#size-cells = < 0x0 >;

reg = < 0x9000 0x1000 >;

clock-frequency = < 0x186a0 >;

interrupts = < 0x9 0x1 >;

status = "okay";

label = "I2C_1";

compatible = "nordic,nrf-twim";

sda-pin = < 0x1e >;

scl-pin = < 0x1f >;

adi_adxl372: adxl372@53 {

compatible = "adi,adxl372";

reg = < 0x53 >;

label = "ADXL372";

int1-gpios = < &gpio0 0xb 0x0 >;

};

ti_hdc20x0: hdc20x0@41 {

compatible = "ti,hdc20x0";

reg = < 0x41 >;

label = "HDC2022";

drdy-gpios = < &gpio0 0xc 0x1 >;

};

};

i2c2: i2c@b000 {

#address-cells = < 0x1 >;

#size-cells = < 0x0 >;

reg = < 0xb000 0x1000 >;

clock-frequency = < 0x186a0 >;

interrupts = < 0xb 0x1 >;

status = "disabled";

label = "I2C_2";

};

i2c3: i2c@c000 {

#address-cells = < 0x1 >;

#size-cells = < 0x0 >;

reg = < 0xc000 0x1000 >;

clock-frequency = < 0x186a0 >;

interrupts = < 0xc 0x1 >;

status = "disabled";

label = "I2C_3";

};

spi0: spi@8000 {

#address-cells = < 0x1 >;

#size-cells = < 0x0 >;

reg = < 0x8000 0x1000 >;

interrupts = < 0x8 0x1 >;

status = "disabled";

label = "SPI_0";

};

spi1: spi@9000 {

#address-cells = < 0x1 >;

#size-cells = < 0x0 >;

reg = < 0x9000 0x1000 >;

interrupts = < 0x9 0x1 >;

status = "disabled";

label = "SPI_1";

};

spi2: spi@b000 {

#address-cells = < 0x1 >;

#size-cells = < 0x0 >;

reg = < 0xb000 0x1000 >;

interrupts = < 0xb 0x1 >;

status = "disabled";

label = "SPI_2";

};

spi3: spi@c000 {

#address-cells = < 0x1 >;

#size-cells = < 0x0 >;

reg = < 0xc000 0x1000 >;

interrupts = < 0xc 0x1 >;

status = "disabled";

label = "SPI_3";

};

spi4: spi@a000 {

compatible = "nordic,nrf-spim";

#address-cells = < 0x1 >;

#size-cells = < 0x0 >;

reg = < 0xa000 0x1000 >;

interrupts = < 0xa 0x1 >;

status = "disabled";

label = "SPI_4";

};

pwm0: pwm@21000 {

compatible = "nordic,nrf-pwm";

reg = < 0x21000 0x1000 >;

interrupts = < 0x21 0x1 >;

status = "okay";

label = "PWM_0";

#pwm-cells = < 0x1 >;

ch0-pin = < 0x1c >;

};

pwm1: pwm@22000 {

compatible = "nordic,nrf-pwm";

reg = < 0x22000 0x1000 >;

interrupts = < 0x22 0x1 >;

status = "disabled";

label = "PWM_1";

#pwm-cells = < 0x1 >;

};

pwm2: pwm@23000 {

compatible = "nordic,nrf-pwm";

reg = < 0x23000 0x1000 >;

interrupts = < 0x23 0x1 >;

status = "disabled";

label = "PWM_2";

#pwm-cells = < 0x1 >;

};

pwm3: pwm@24000 {

compatible = "nordic,nrf-pwm";

reg = < 0x24000 0x1000 >;

interrupts = < 0x24 0x1 >;

status = "disabled";

label = "PWM_3";

#pwm-cells = < 0x1 >;

};

gpio0: gpio@842500 {

compatible = "nordic,nrf-gpio";

gpio-controller;

reg = < 0x842500 0x300 >;

#gpio-cells = < 0x2 >;

label = "GPIO_0";

status = "okay";

port = < 0x0 >;

phandle = < 0x2 >;

};

gpio1: gpio@842800 {

compatible = "nordic,nrf-gpio";

gpio-controller;

reg = < 0x842800 0x300 >;

#gpio-cells = < 0x2 >;

ngpios = < 0x10 >;

label = "GPIO_1";

status = "okay";

port = < 0x1 >;

};

qspi: qspi@2b000 {

compatible = "nordic,nrf-qspi";

#address-cells = < 0x1 >;

#size-cells = < 0x0 >;

reg = < 0x2b000 0x1000 >;

interrupts = < 0x2b 0x1 >;

status = "okay";

label = "QSPI";

sck-pin = < 0x11 >;

io-pins = < 0xd >, < 0xe >, < 0xf >, < 0x10 >;

csn-pins = < 0x12 >;

mx25r64: mx25r6435f@0 {

compatible = "nordic,qspi-nor";

reg = < 0x0 >;

writeoc = "pp4io";

readoc = "read4io";

sck-frequency = < 0x7a1200 >;

label = "MX25R64";

jedec-id = [ C2 28 17 ];

sfdp-bfp = [ E5 20 F1 FF FF FF FF 03 44 EB 08 6B 08 3B 04 BB EE FF FF FF FF FF 00 FF FF FF 00 FF 0C 20 0F 52 10 D8 00 FF 23 72 F5 00 82 ED 04 CC 44 83 68 44 30 B0 30 B0 F7 C4 D5 5C 00 BE 29 FF F0 D0 FF FF ];

size = < 0x4000000 >;

has-dpd;

t-enter-dpd = < 0x2710 >;

t-exit-dpd = < 0x88b8 >;

};

};

rtc0: rtc@14000 {

compatible = "nordic,nrf-rtc";

reg = < 0x14000 0x1000 >;

cc-num = < 0x4 >;

interrupts = < 0x14 0x1 >;

status = "okay";

clock-frequency = < 0x8000 >;

prescaler = < 0x1 >;

label = "RTC_0";

};

rtc1: rtc@15000 {

compatible = "nordic,nrf-rtc";

reg = < 0x15000 0x1000 >;

cc-num = < 0x4 >;

interrupts = < 0x15 0x1 >;

status = "okay";

clock-frequency = < 0x8000 >;

prescaler = < 0x1 >;

label = "RTC_1";

};

clock: clock@5000 {

compatible = "nordic,nrf-clock";

reg = < 0x5000 0x1000 >;

interrupts = < 0x5 0x1 >;

status = "okay";

label = "CLOCK";

};

power: power@5000 {

compatible = "nordic,nrf-power";

reg = < 0x5000 0x1000 >;

interrupts = < 0x5 0x1 >;

status = "okay";

};

wdt: wdt0: watchdog@18000 {

compatible = "nordic,nrf-watchdog";

reg = < 0x18000 0x1000 >;

interrupts = < 0x18 0x1 >;

status = "okay";

label = "WDT";

};

wdt1: watchdog@19000 {

compatible = "nordic,nrf-watchdog";

reg = < 0x19000 0x1000 >;

interrupts = < 0x19 0x1 >;

status = "disabled";

label = "WDT_1";

};

timer0: timer@f000 {

compatible = "nordic,nrf-timer";

status = "okay";

reg = < 0xf000 0x1000 >;

cc-num = < 0x6 >;

interrupts = < 0xf 0x1 >;

prescaler = < 0x0 >;

label = "TIMER_0";

};

timer1: timer@10000 {

compatible = "nordic,nrf-timer";

status = "okay";

reg = < 0x10000 0x1000 >;

cc-num = < 0x6 >;

interrupts = < 0x10 0x1 >;

prescaler = < 0x0 >;

label = "TIMER_1";

};

timer2: timer@11000 {

compatible = "nordic,nrf-timer";

status = "okay";

reg = < 0x11000 0x1000 >;

cc-num = < 0x6 >;

interrupts = < 0x11 0x1 >;

prescaler = < 0x0 >;

label = "TIMER_2";

};

usbd: usbd@36000 {

compatible = "nordic,nrf-usbd";

reg = < 0x36000 0x1000 >;

interrupts = < 0x36 0x1 >;

num-bidir-endpoints = < 0x1 >;

num-in-endpoints = < 0x7 >;

num-out-endpoints = < 0x7 >;

num-isoin-endpoints = < 0x1 >;

num-isoout-endpoints = < 0x1 >;

status = "okay";

label = "USBD";

};

};

gpiote: gpiote@4002f000 {

compatible = "nordic,nrf-gpiote";

reg = < 0x4002f000 0x1000 >;

interrupts = < 0x2f 0x5 >;

status = "okay";

label = "GPIOTE_1";

};

cryptocell_sw: cryptocell-sw {

compatible = "nordic,nrf-cc312-sw";

#address-cells = < 0x0 >;

label = "CRYPTOCELL_SW";

};

};

cpus {

#address-cells = < 0x1 >;

#size-cells = < 0x0 >;

cpu@0 {

device_type = "cpu";

compatible = "arm,cortex-m33f";

reg = < 0x0 >;

#address-cells = < 0x1 >;

#size-cells = < 0x1 >;

mpu: mpu@e000ed90 {

compatible = "arm,armv8m-mpu";

reg = < 0xe000ed90 0x40 >;

arm,num-mpu-regions = < 0x8 >;

};

};

};

leds {

compatible = "gpio-leds";

led0: led_0 {

gpios = < &gpio0 0x1c 0x1 >;

label = "Green LED 0";

};

led1: led_1 {

gpios = < &gpio0 0x1d 0x1 >;

label = "Green LED 1";

};

led2: led_2 {

gpios = < &gpio0 0x1e 0x1 >;

label = "Green LED 2";

};

led3: led_3 {

gpios = < &gpio0 0x1f 0x1 >;

label = "Green LED 3";

};

};

buttons {

compatible = "gpio-keys";

button0: button_0 {

gpios = < &gpio0 0x17 0x11 >;

label = "Push button 1";

};

button1: button_1 {

gpios = < &gpio0 0x18 0x11 >;

label = "Push button 2";

};

button2: button_2 {

gpios = < &gpio0 0x8 0x11 >;

label = "Push button 3";

};

button3: button_3 {

gpios = < &gpio0 0x9 0x11 >;

label = "Push button 4";

};

};

reserved-memory {

#address-cells = < 0x1 >;

#size-cells = < 0x1 >;

ranges;

sram0_image: image@20000000 {

reg = < 0x20000000 0x70000 >;

};

sram0_s: image_s@20000000 {

reg = < 0x20000000 0x40000 >;

};

sram0_ns: image_ns@20040000 {

reg = < 0x20040000 0x30000 >;

};

sram0_shared: memory@20070000 {

reg = < 0x20070000 0x10000 >;

};

};

};

SDK and Build Versions:

nRF Connect SDK: v1.5.1

Zephyr OS: 2.4.99