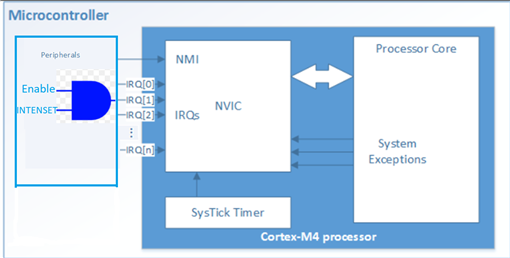

Trying to understand how interrupts work on nRF52: does setting an INTENSET register of the said peripheral enable the interrupt, and to propagate the interrupt over the Cortex M4, the NVIC_ISERx register needs to be set as well?

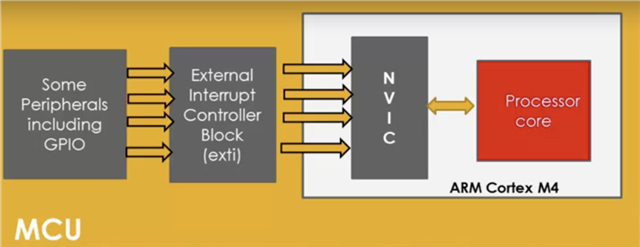

Is the idea similar to the depiction below where INTENSET is a part of the EXTI?