Hi:

SW: NCS v2.5.0

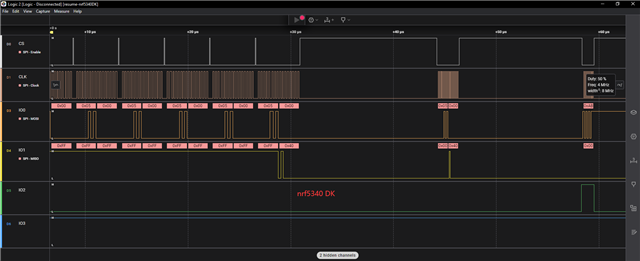

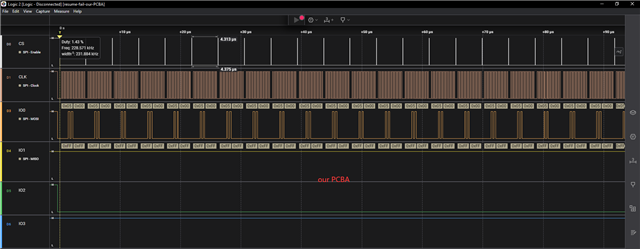

HW: nRF5340 + flash gd25q256e

To reduce the power consumption of the QSPI flash, we have two approaches.

1. cut off the QSPI flash's power when the product is in sleep mode (the power can be turned on/off by an LDO)

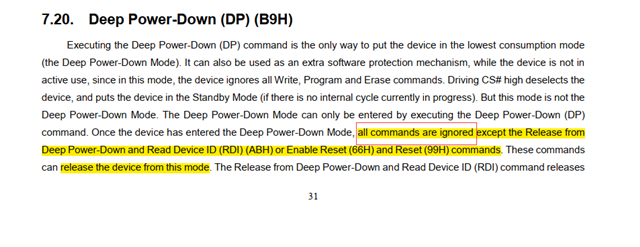

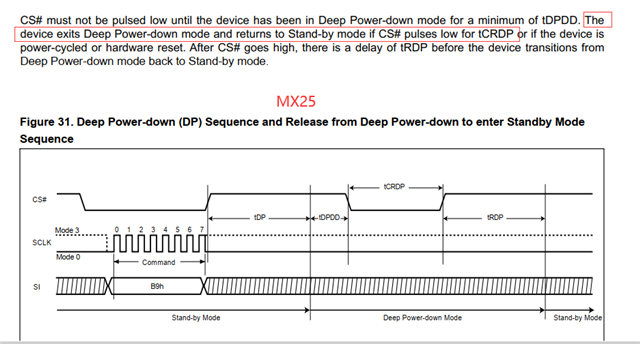

2. always keep the power of the QSPI flash, and put the flash into deep power down mode when the product is in sleep mode.

unfortunately, both of these two approaches have problems.

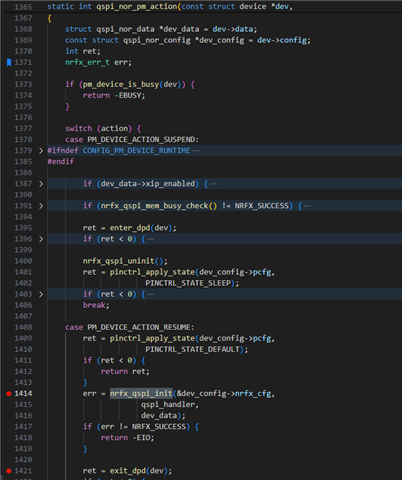

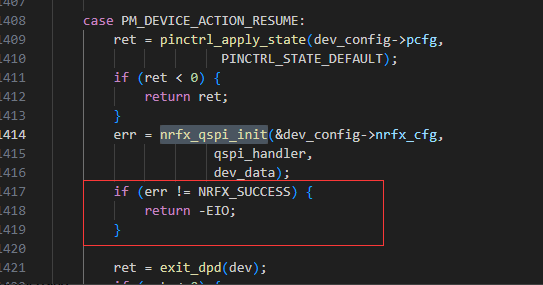

for approach 1, when turning on the power again, and initiating the QSPI and XIP again, the XIP doesn't work.

e.g

below is the QSPI configuration

&qspi {

status = "okay";

pinctrl-0 = <&qspi_default>;

pinctrl-1 = <&qspi_sleep>;

pinctrl-names = "default", "sleep";

gd25q256: gd25q256e@0 {

compatible = "nordic,qspi-nor";

reg = <0>;

/* GD25Q256 supports only pp(cmd 02H) and pp4o(cmd 32H) */

writeoc = "pp4o";

/* GD25Q256 supports all readoc options */

readoc = "read4io";

sck-frequency = <8000000>;

jedec-id = [c8 40 19];

sfdp-bfp = [/*read the sfdp-bfp by jesd216 sample(zephyr\samples\drivers\jesd216)*/

e5 20 f3 ff ff ff ff 0f 44 eb 08 6b 08 3b 42 bb

ee ff ff ff ff ff 00 ff ff ff 00 ff 0c 20 0f 52

10 d8 00 ff d6 39 a5 fe 83 1f 15 51 ec 62 16 33

7a 75 7a 75 04 bd d5 5c 00 06 64 00 08 50 00 01

];

size = <268435456>;

has-dpd;

t-enter-dpd = <40000>;

t-exit-dpd = <45000>;

enter-4byte-addr = <0x01>;

address-size-32;

};

};

Do you have any ideas on this issue?

Thanks!