Hello,

I am using the following device and development kit:

- Device: NORA-B106-00B (nRF5340)

- nRF Connect SDK: 2.0.2

Currently, I am trying to use GPIOTE PORT events to detect interrupts on pins P0.04 and P0.28.

The mask for pins that do not use GPIOTE is defined in the Devicetree as follows:

&gpio0 {

status = "okay";

sense-edge-mask = < 0x10000010 >; //Mask GPIOTE events other than P0.04 and P0.28

};

Also, among the pins that mask GPIOTE events are the following pins used as SPIM4.

- P0.08/SCK

- P0.09/MOSI

- P0.10/MISO

- P0.11/CSN

I have PSRAM connected to SPIM4, which is turned off when idle and turned on when in use.

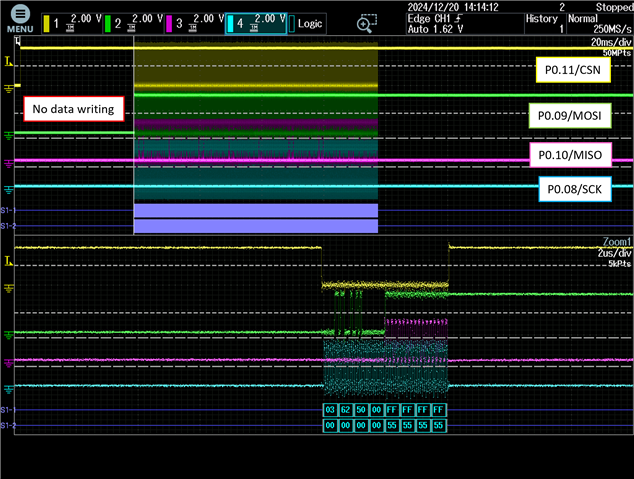

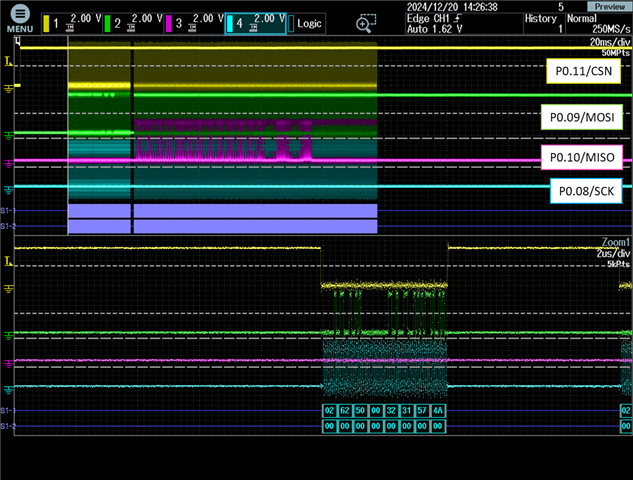

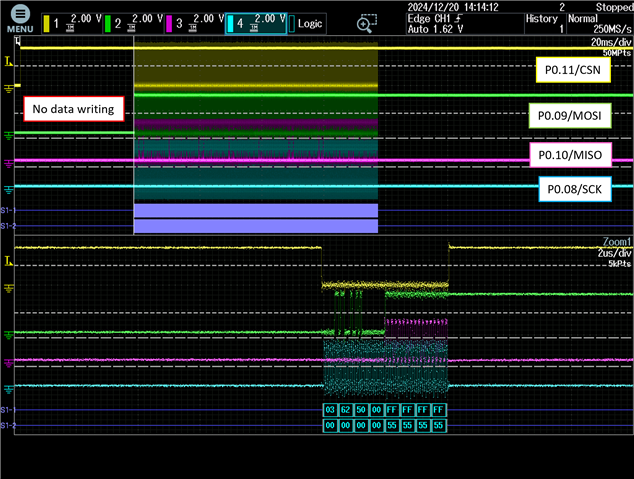

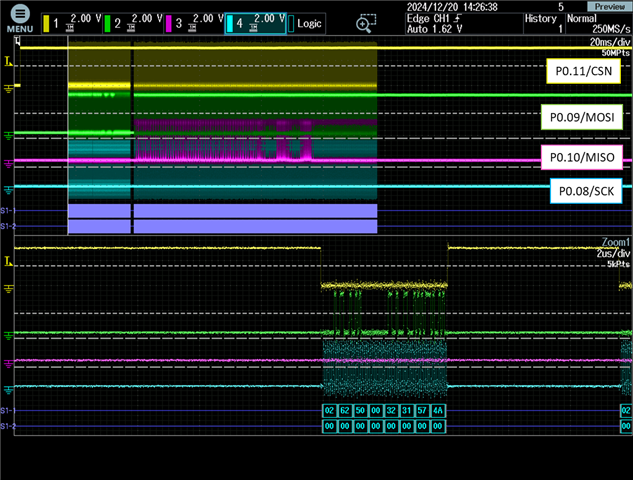

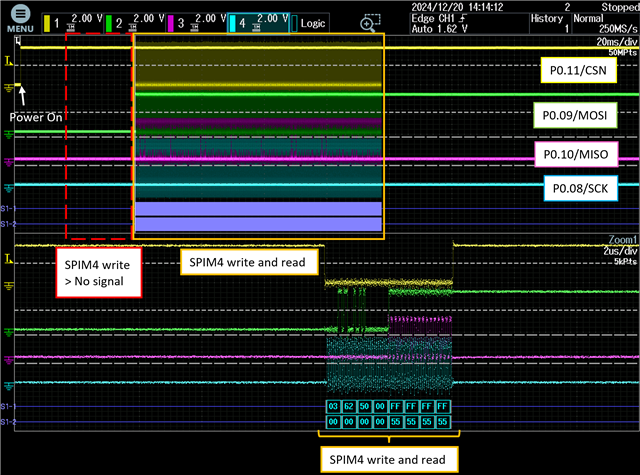

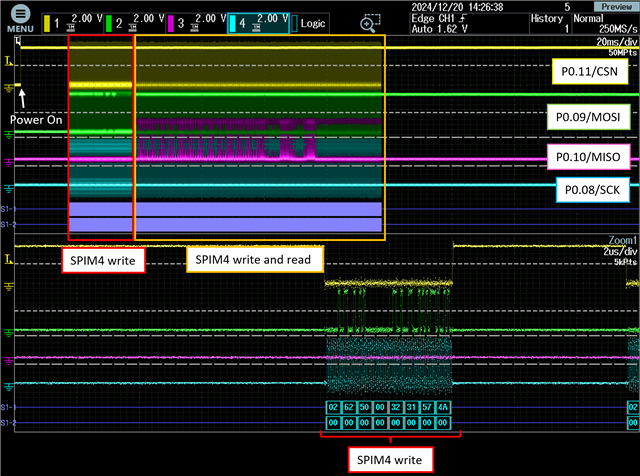

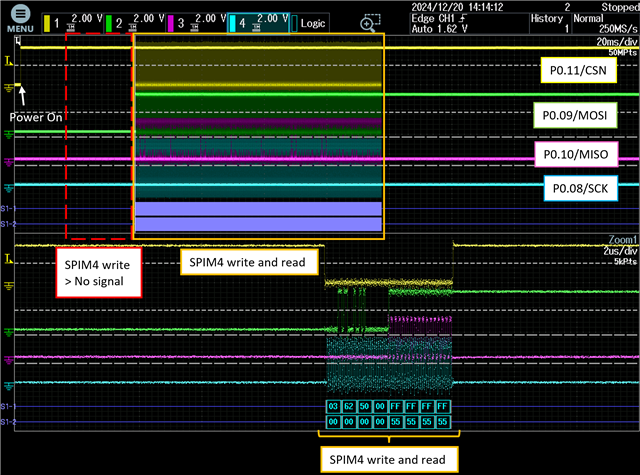

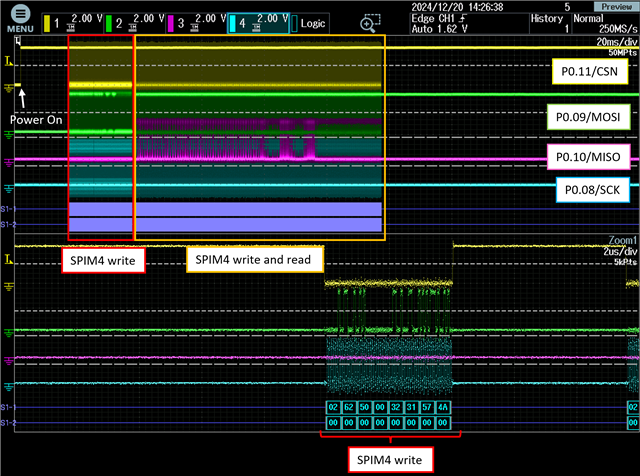

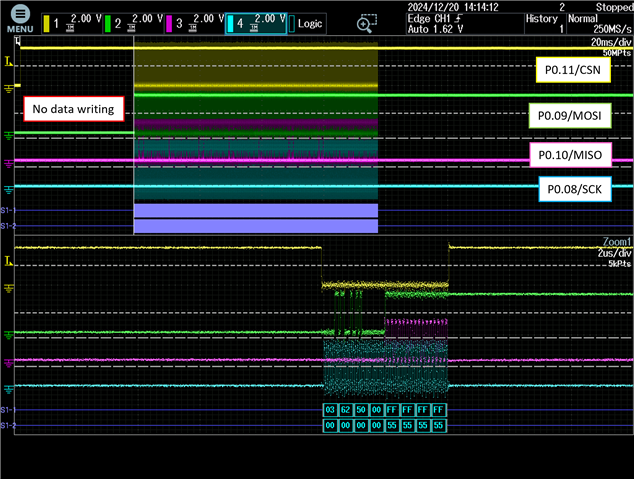

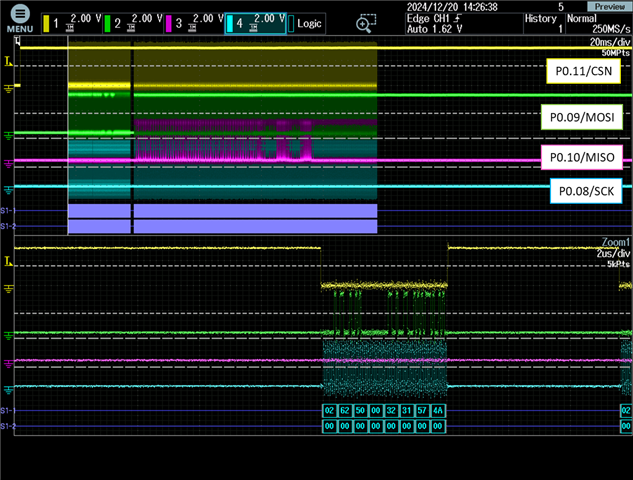

Here, if you try to write data using the nrfx spim driver after the power is turned on (P0.11/CSN:High), the write will not be executed as shown below, but if you read the data immediately after, the SPIM4 works and reads the data.

(Since no data has been written, the data read will be an undefined value.)

Also, even if you change the hardware to always have the PSRAM powered on (P0.11/CSN:Always High), the above procedure will not execute the first data write.

If you comment out "sense-edge-mask" in the Device Tree, the problem of this data not being written does not occur.

(It is possible that other pins are also behaving abnormally, but I have not been able to confirm this at present.)

Questions:

- If I mask the GPIOTE event in Devicetree as above, could it affect other peripherals such as SPIM?

- Is there another way to properly configure GPIOTE PORT events?

Best regard,