Hi DevZone,

I am using the nRF52840 to interface an ADS1298 (ECG Chip) via SPI.

I want to test if the communication between the devices are working by:

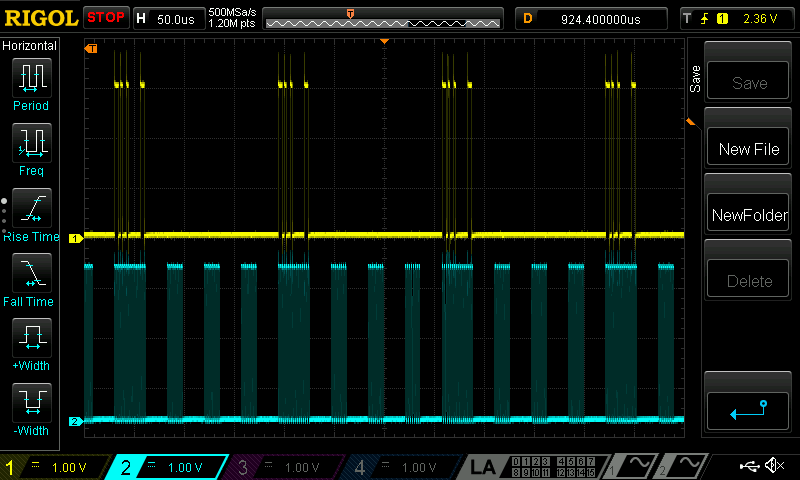

- Sending a RREG (Read From Register) opcode from the nRF52840 to the ADS1298

- And then read its ID Register.

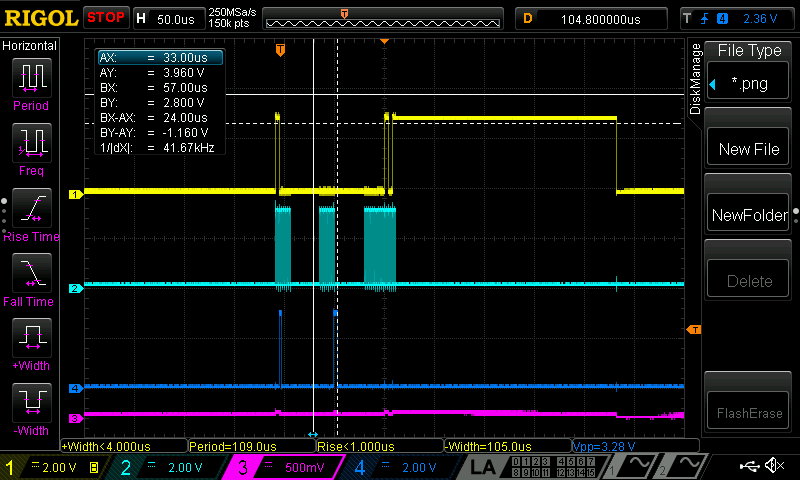

The RREG command is two bytes long, and for multi-byte commands the following needs to be done:

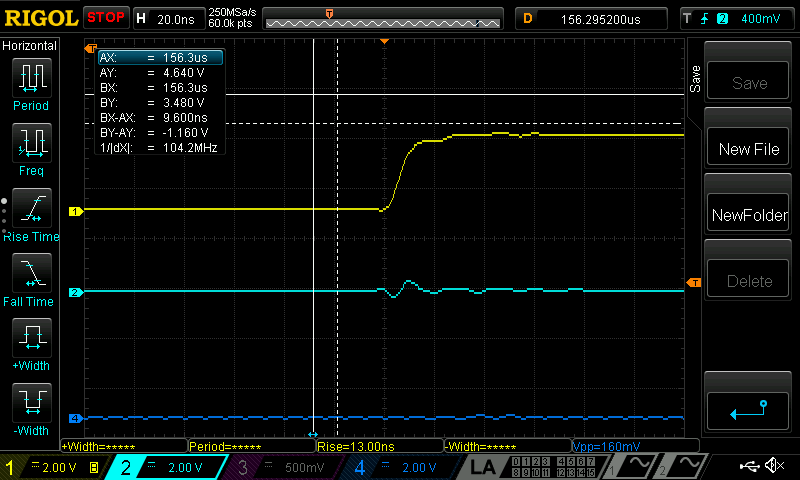

1. Send the first byte and then wait for 4 * tCLK before sending the next byte.

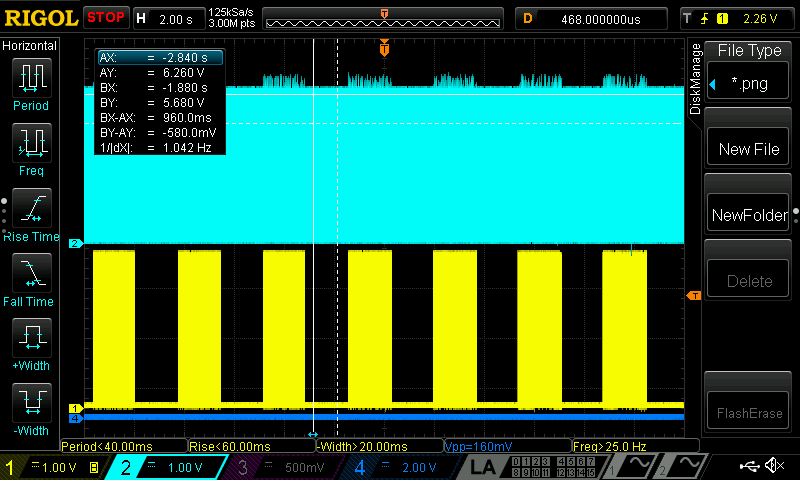

2. The CS (or SS) pin needs to be held low during the entire session for both transfer and receive.

I am trying to test this with the example provided in the nRF5 SDK 15.3 by using this function:

- nrf_drv_spi_transfer(&spi, m_tx_buf, m_length, m_rx_buf, m_length);

My problem is that:

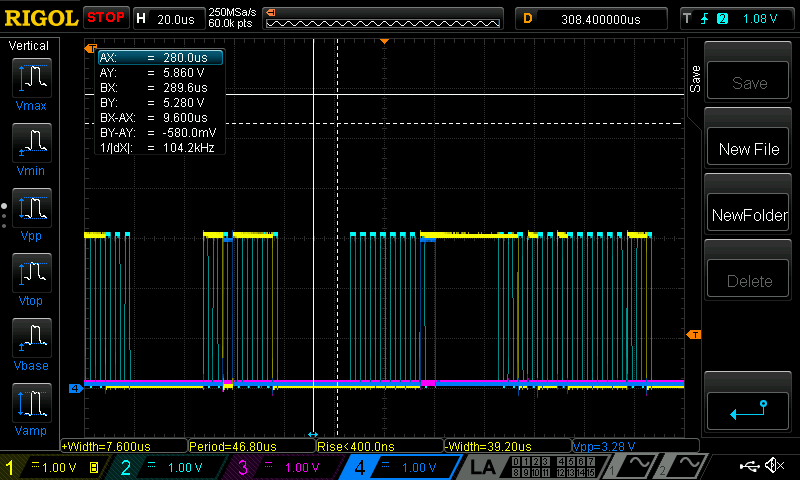

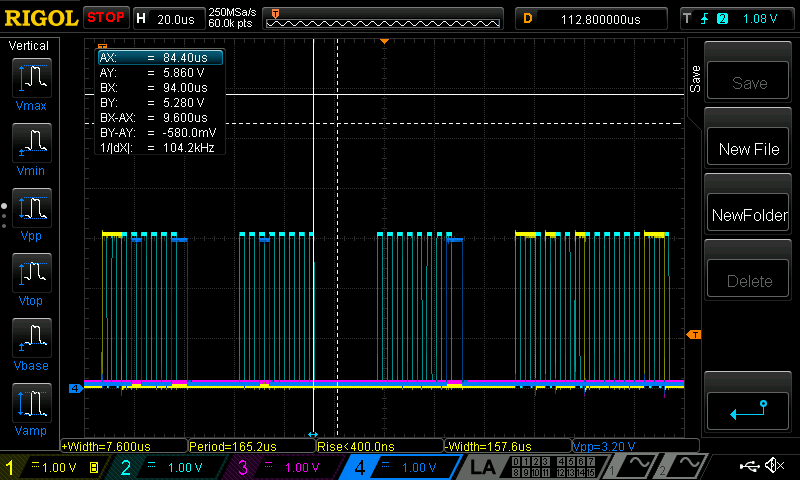

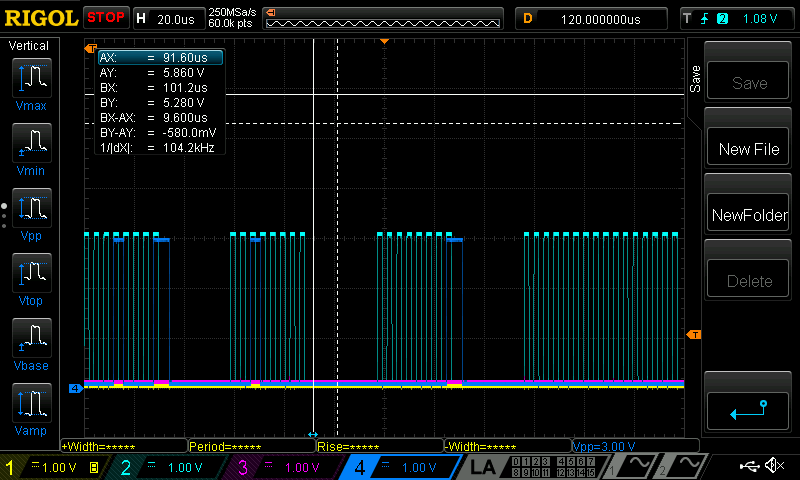

- I cannot insert a delay between the bytes when using the nrf_drv_spi_tranfer() for multiple byte transfers

- If i use separate calls of the nrf_drv_spi_transfer() for each byte, then the CS pin is not held low.

Is there any way I can use this driver to send multiple bytes with a fixed delay between them, without the CS pin going high during the session?

Thank you for reading

Br. Casper