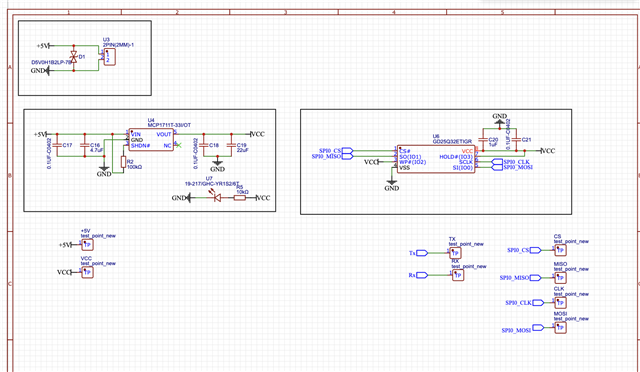

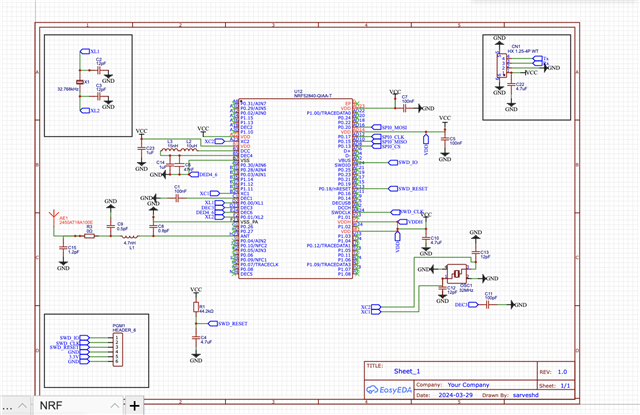

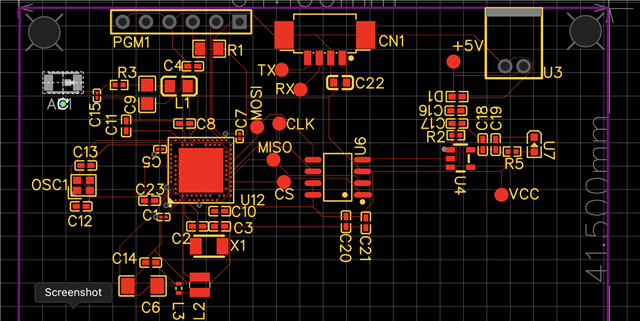

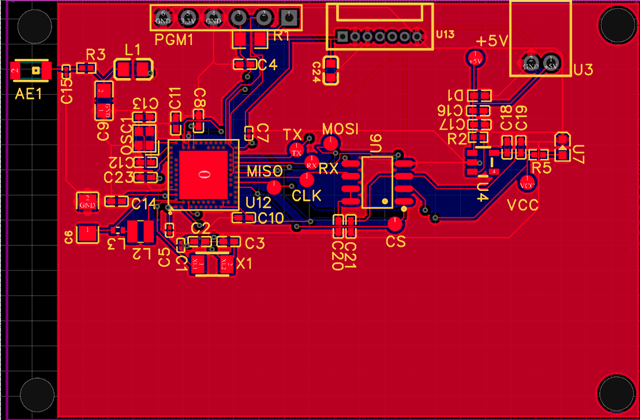

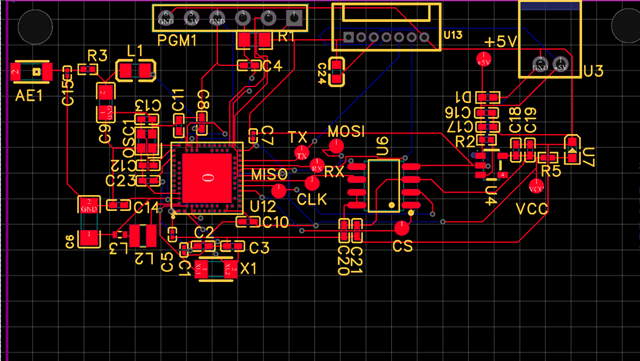

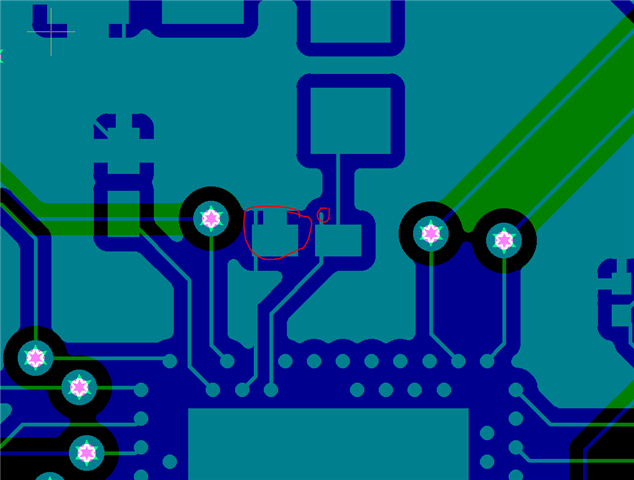

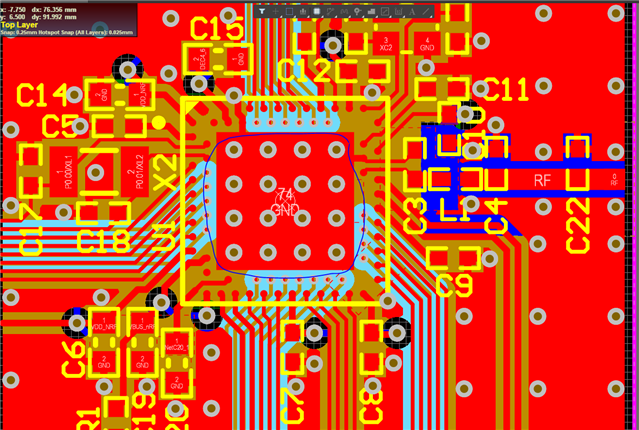

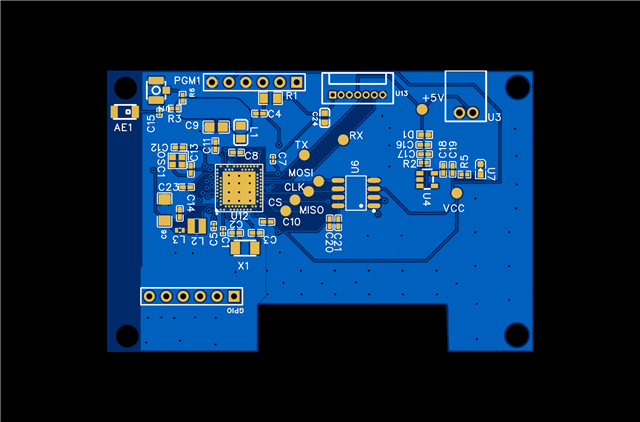

Hi, I am new to PCB design, so I want suggestions for my designed PCB. Please review it once and provide feedback upon that. I am making this PCB to use this with Thread and matter-related products. I have used EasyEda to design the PCB and used the reference designs provided by Nordic.

General PCB design guidelines for nRF52 series

.

.